I. Avertissement▲

Notez que je décline toute responsabilité quant aux conséquences que pourrait avoir la mise en pratique de ce tutoriel. Les composants de la carte sont sensibles et n’apprécieront pas une mauvaise tension sur leurs broches ou que vous mettiez celles-ci en court-circuit suite à une mauvaise configuration chargée dans le FPGA.

II. Installation de Quartus▲

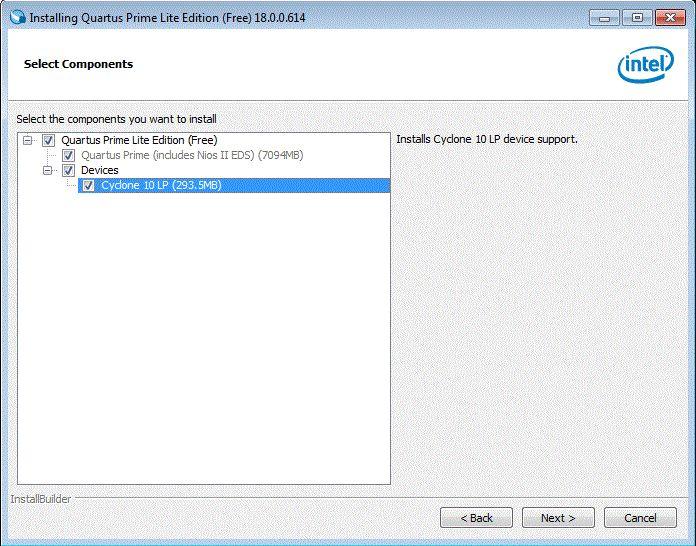

Le FPGA étant un ALTERA Cyclone 10LP, commencez par installer le logiciel Quartus :

- allez sur la page de téléchargement d’INTEL/ALTERA et choisissez la dernière version de Quartus en version Lite ;

- les éléments à télécharger sont, au minimum, Quartus Prime (includes Nios II EDS) et Cyclone 10 LP device support. Placez-les dans le même répertoire.

- si vous ne disposez pas déjà d’un compte ALTERA, vous aurez certainement besoin de vous inscrire.

Si vous pensez utiliser un boîtier USB BLASTER pour la programmation en direct du FPGA, vous pourriez avoir besoin du package « Quartus II Programmer and SignalTap II » de la version Web Edition 13.0.

Une fois le téléchargement effectué, lancez l’installation de Quartus (QuartusLiteSetup-xx.yy-windows.exe).

Si, par défaut, l’installation ne le propose pas, sélectionnez le support du Cyclone 10LP dans la boite de dialogue suivante :

III. Projet Arduino de base▲

Il nous faut ensuite avoir une base de projet avec les configurations d’E/S de la carte ARDUINO.

Vous pourrez trouver celle-ci à cet emplacement.

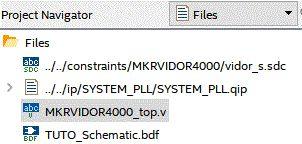

Décompressez le fichier ZIP et ouvrez avec Quartus (File → Open Project) le fichier MKRVIDOR4000.qpf.

Celui-ci se trouve sous l’arborescence : …\VidorFPGA-master\projects\MKRVIDOR4000_template.

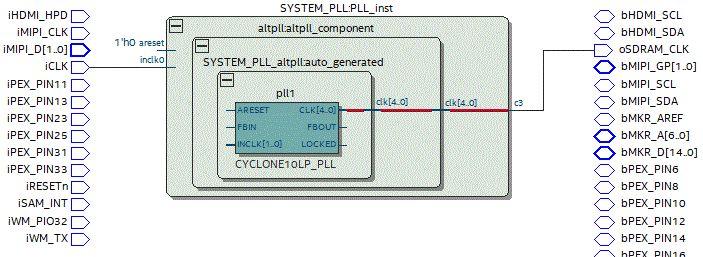

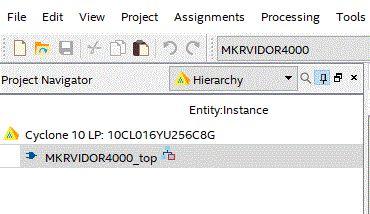

Le module de plus haut niveau « Top level entity » est pour ce projet le module MKRVIDOR4000_top.

Ce fichier définit :

- le nom des signaux d’E/S et leur direction (input, output, inout…) ;

- les liaisons internes (Wire), les buffers ou registres (reg)… ;

- les instances d’autres modules (ici cyclone10lp_oscillator et SYSTEM_PLL) ;

- les règles combinatoires (assign) ou séquentielles (always/begin/end).

Un autre fichier indispensable est celui qui met en relation les signaux d’E/S avec le brochage du FPGA. Ce fichier définit également les niveaux de tension de ces signaux, donc NE LE MODIFIEZ PAS.

Vous pouvez le visualiser en sélectionnant « Assignments → Assignments Editor ».

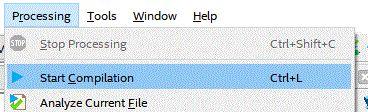

Si vous compilez le projet (Processing → Start compilation), et regardez l’architecture générée (Tools → Netlist viewers → RTL viewer), vous constaterez que le projet ne contient pour le moment que peu de chose.

IV. Clignotement d’une LED▲

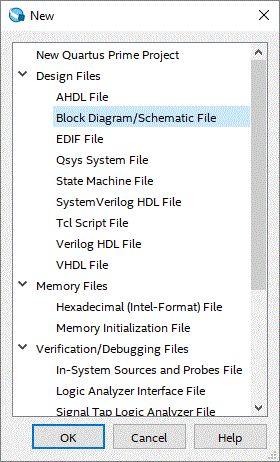

Nous allons ajouter une feuille de schéma à ce projet. Faites File→New et choisissez « Block Diagram/Schematic File » :

S’ouvre alors une feuille dans laquelle nous allons pouvoir ajouter et connecter des composants comme sur un schéma électronique.

IV-A. Ajout des E/S▲

Pour faire clignoter notre LED nous avons besoin d’un port d’entrée (une horloge), et d’un port de sortie (le signal de la LED).

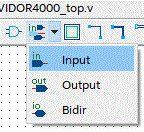

Ajoutez ces ports (1 Input + 1 Output) sur la feuille en cliquant sur l’icône suivante :

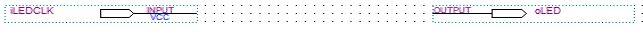

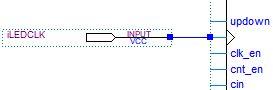

Puis, soit en cliquant deux fois sur le nom, soit en faisant un clic droit et « Properties », renommez l’entrée « iLEDCLK » et la sortie « oLED » :

Avant d’ajouter toute la logique nécessaire entre ces deux ports, sauvegardez le schéma (CTRL+S) sous le nom « TUTO_Schematic.bdf ».

L’horloge que nous allons utiliser en entrée est celle fournie par l’oscillateur interne du Cyclone 10. Celle-ci a une fréquence d’environ 80 Mhz, ce qui est beaucoup trop élevé pour notre besoin. Plutôt que d’utiliser une PLL en diviseur de fréquence, nous allons ici lui préférer un compteur.

À chaque coup d’horloge en entrée, le compteur sera incrémenté. Chacun des bits du compteur changera donc d’état à une fréquence qui lui sera propre : Freq_bit_n = (Freq_entrée / (2 ^ (n+1))).

Pour un clignotement toutes les secondes, il faudra prendre n=25.

IV-B. Ajout du compteur▲

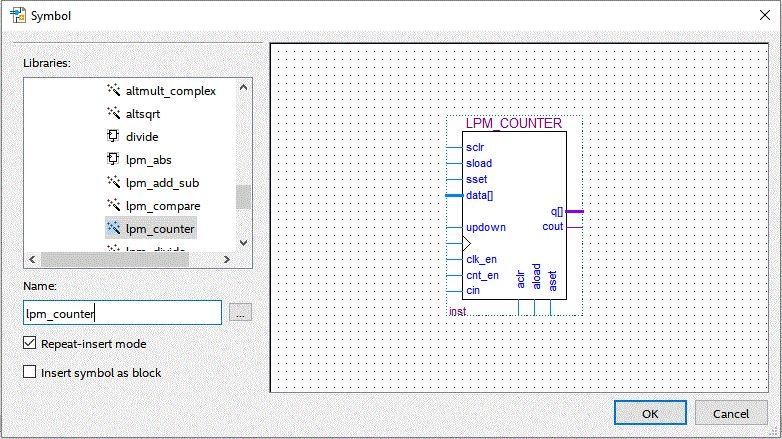

Pour ajouter le compteur, appuyez sur l’icône « Symbol Tool » :

Sélectionnez un LPM_COUNTER et cliquez sur « OK » pour le positionner dans le schéma :

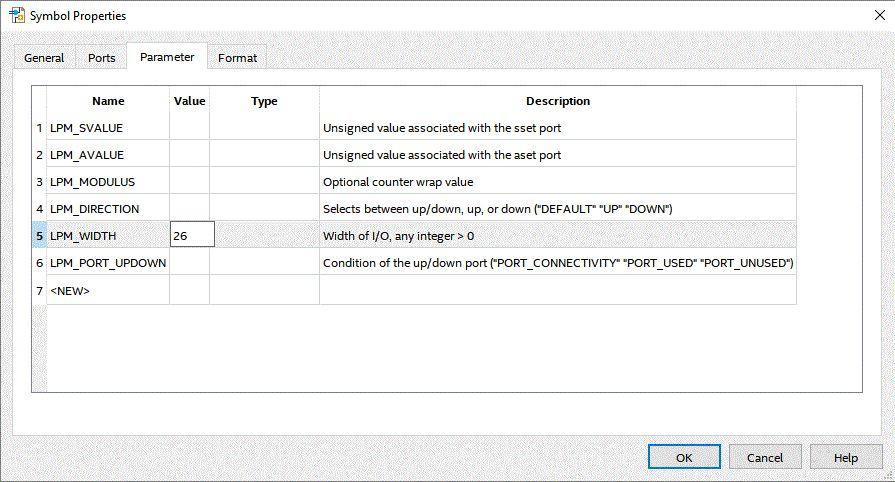

Éditez ensuite les propriétés du compteur (clic droit + « Properties ») et entrez la valeur 26 pour LPM_WIDTH :

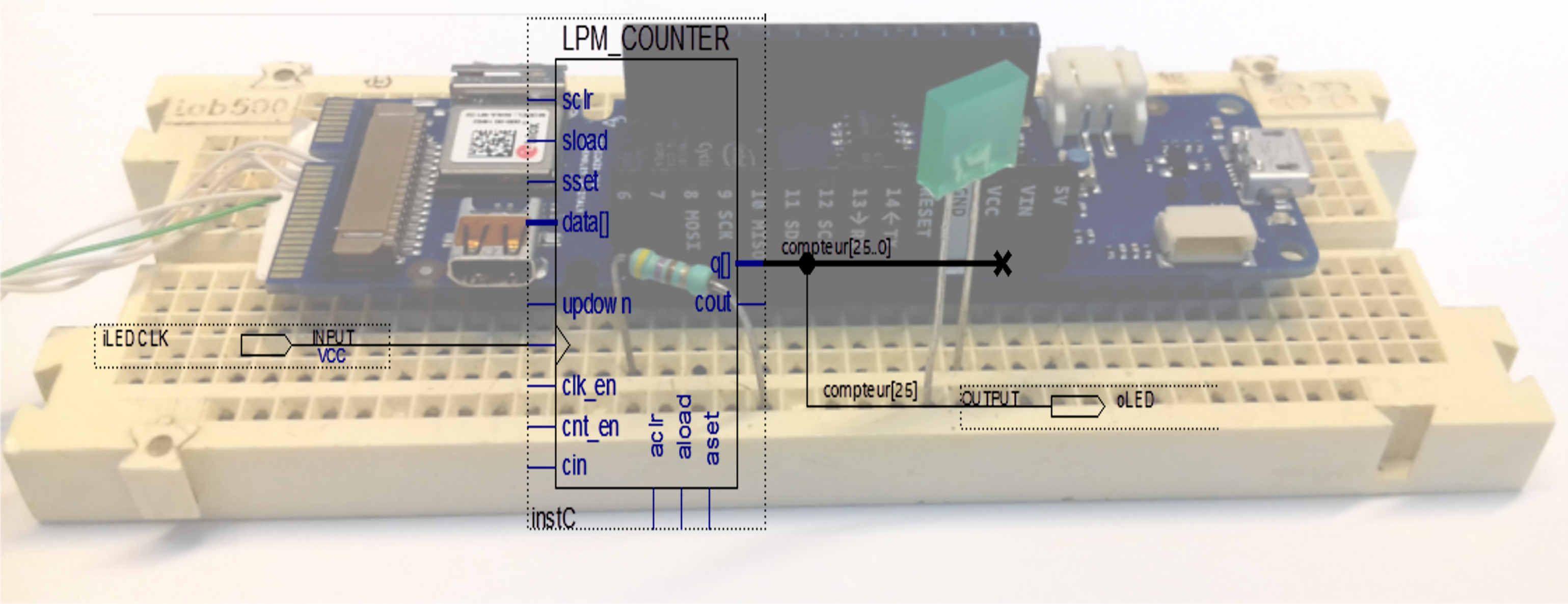

IV-C. Finalisation du schéma▲

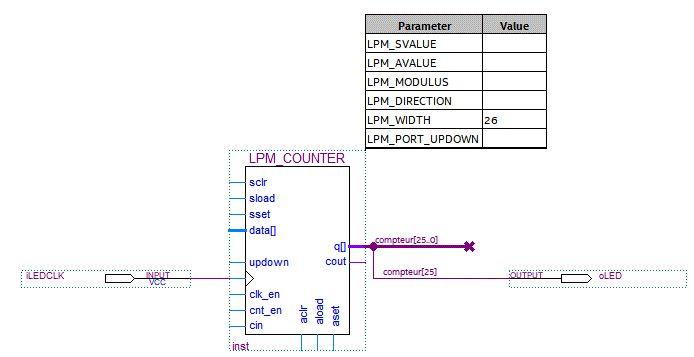

Vous allez ensuite :

-

relier l’entrée iLEDCLK à l’horloge du compteur en utilisant la commande « Node Tool » :

-

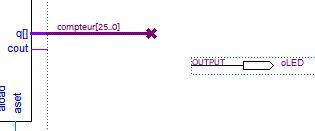

sortir un bus de données depuis la sortie q[] du compteur avec la commande « Bus Tool » :

-

nommer ce bus « compteur[25..0] » (Clic droit sur le bus et « Properties ») :

- et finalement relier (avec l’outil Node Tool) la sortie oLED au bus compteur.

Comme seulement un des signaux du bus nous intéresse, vous devez dire à Quartus lequel prendre en le nommant (ici : compteur[25]).

Vous en avez fini avec le schéma. Sauvegardez-le !

IV-D. Compilation▲

La prochaine étape sera d’inclure ce schéma dans le « Top level entity » du projet.

Pour cela, double-cliquez sur le fichier MKRVIDOR4000_top.v :

et ajoutez-y les lignes suivantes (au-dessus de reg [5:0] rRESETCNT;) :

TUTO_Schematic TUTO_Schematic_inst

(

.iLEDCLK(wOSC_CLK) , // L’entrée d’horloge est reliée à l’oscillateur interne 80Mhz

.oLED(bMKR_D[6]) // La sortie LED est reliée à la broche 6 du port MKR

);Il ne vous reste plus qu’à recompiler le projet :

IV-E. Création du fichier app.h et intégration dans le sketch▲

La compilation a généré un fichier MKRVIDOR4000.ttf dans le répertoire output_files. Ce fichier liste, au format texte, les octets décrivant la configuration du FPGA.

Il va falloir inverser bit à bit chacun de ces octets avant de l’envoyer à la carte ARDUINO.

Pour cela, téléchargez le logiciel écrit en Java disponible ici : ReverseByte_V2.zip

Exécutez la ligne de commande java ReverseByte MKRVIDOR4000.ttf app.h.

Cela va générer le fichier app.h que vous pourrez inclure dans le sketch vide disponible ici : EmptySketch.zip.

Il ne vous reste plus qu’à charger le sketch dans la carte avec l’IDE Arduino.

- En aucun cas vous ne devez reconfigurer le port PA20 du SAMD21 en sortie. Celui-ci est déjà utilisé en sortie par le FPGA.

- Le port PA20 (nommé bMKR_D[6] coté FPGA) correspond à la broche 1 du connecteur J5 (notée « 6 »). Vous devez connecter une LED en série avec une résistance de valeur appropriée entre cette broche et la masse (GND) pour voir clignoter la LED.

Dans la prochaine partie de ce tutoriel, nous verrons comment implémenter un bloc PWM, et le paramétrer via le SAMD21.

V. Annexe : les fichiers du projet Blink▲

ReverseByte_V2 : Version compilée avec Java 1.8, et incluant le code source.

EmptySketch : Sketch chargeant uniquement le fichier de configuration app.h (non inclus).

FPGABlinkLED : Projet Quartus.

FPGABlinkLED_Sketch : Sketch incluant le fichier app.h.

VI. Note de la rédaction Developpez▲

Cet article est une mise à jour par l'auteur lui-même d'un article initialement posté sur son blog https://www.systemes-embarques.fr/.

Merci à f-leb et à naute pour la mise en page et les corrections.